# Modern C++ White paper:

## Making things do stuff

Glennan Carnie Technical consultant, Feabhas

## Introduction

C has long been the language of choice for smaller, microcontroller-based embedded systems; particularly for close-to-the-metal hardware manipulation.

C++ was originally conceived with a bias towards systems programming; performance and efficiency being key design highlights. Traditionally, many of the advancements in compiler technology, optimisation, etc., had centred around generating code for PC-like platforms (Linux, Windows, etc). In the last few years C++ compiler support for microcontroller targets has advanced dramatically, to the point where Modern C++ is an increasingly attractive language for embedded systems development.

In this whitepaper we will explore how to use Modern C++ to manipulate hardware on a typical embedded microcontroller. We'll see how you can use C++'s features to hide the actual underlying hardware of our target system and provide an abstract hardware API that developers can work to. We'll explore the performance (in terms of memory and code size) of these abstractions compared to their C counterparts.

### Contents

| Basic concepts                                     | 3  |

|----------------------------------------------------|----|

| General-Purpose Input-Ouput (GPIO)                 | 15 |

| An object-based approach                           | 23 |

| Implementation                                     | 32 |

| Placement new                                      | 41 |

| Generic register types                             | 48 |

| Dealing with read-only and write-only registers    |    |

| Bit proxies                                        | 64 |

| Revisiting read-only and write-only register types | 72 |

| Summary                                            | 82 |

## **Basic concepts**

We'll begin by having a look at the very basics of hardware manipulation – accessing hardware devices and bit manipulation.

#### Port vs memory-mapped I/O

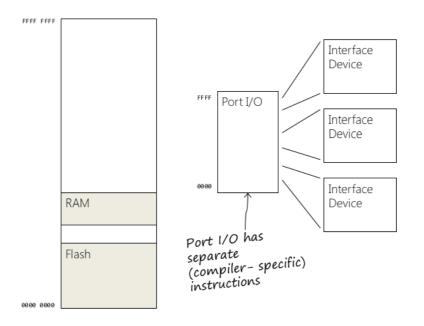

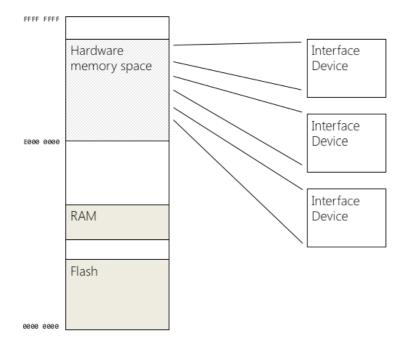

Memory-Mapped Input/Output (MMIO) and port Input/Output (also called port-mapped I/O or PMIO) are two complementary methods of performing input/output between the CPU and I/O devices in a target.

PMIO uses a special class of CPU instructions specifically for performing I/O. This is generally found on Intel microprocessors, specifically the IN and OUT instructions which can read and write a single byte to an I/O device. I/O devices have a separate address space from general memory, either accomplished by an extra "I/O" pin on the CPU's physical interface, or an entire bus dedicated to I/O.

PMIO is usually accessed via special compiler-specific intrinsic functions; that is, non-standard C++. For that reason, I'll exclude PMIO from this discussion.

MMIO uses the same bus to address both memory and I/O devices, and the CPU instructions used to read and write to memory are also used in accessing I/O devices. In order to accommodate the I/O devices, areas of CPU addressable space must be reserved for I/O rather than memory. The I/O devices monitor the CPU's address bus and respond to any CPU access of their assigned address space, mapping the address to their hardware registers.

It is important to note that the two techniques are not normally found on same architecture; although for example on older PCs video ram would be memory mapped and all other I/O devices would be port I/O.

#### Accessing hardware from C++

The problem from a language perspective is that the compiler can only see objects that have been declared; and by definition those objects with be in the memory areas. There is no direct way of accessing I/O addresses from C++. The way round this is to *indirectly* access the memory, using pointers.

There are two things to take into consideration with this method:

- We must select a pointer type that matches our hardware register

- We have to 'force' an address into the pointer

The type of a pointer tells the compiler how many bytes to access, how to interpret the bits and the valid behaviours that can be performed on that memory location. In configuration-type registers normally each bit has its own significance; for data-type registers the value is normally held as a 'raw' number. For that reason, hardware access registers should always be qualified as unsigned. The actual type depends on the size of the hardware register.

(Avoid assuming that (for example) a 32-bit register pointer is good enough for all 8-, 16- and 32-bit registers. You risk potentially overwriting adjacent registers; and even adjacent reads could have unintended side effects).

```

unsigned char* reg_8 { }: // 8-bit

unsigned short* reg_16 { }: // 16-bit

unsigned long* reg_32 { }: // 32-bit

```

Note: A 32-bit register (for example) may be accessible (depending on hardware) as either 8-bits, 16-bits or 32-bits.

However, using a pointer-to-32-bit to access an 8-bit register is undefined. You risk overwriting adjacent registers; and even reads could have unintended side-effects (for example, reading some hardware registers has the effect of clearing them)

To be more explicit it's probably good practice to use specific-width aliases:

```

#include <cstdint>

int main()

{

std::uint8_t* reg_8 { };

std::uint16_t* reg_16 { };

std::uint32_t* reg_32 { };

...

}

```

Our next problem is to 'force' a register address into the pointer. As an integral value cannot be assigned to a pointer, we must cast the value. The correct C++ way is using reinterpret\_cast<> (in fact, it's one of the few uses of reinterpret\_cast<>)

```

#include <cstdint>

using std::uint8_t;

using std::uint16_t:

using std::uint32_t:

int main()

{

uint8_t* reg_8 { reinterpret_cast<uint8_t*>(0x40020000) };

uint16_t* reg_16 { reinterpret_cast<uint16_t*>(0x40020010) };

uint32_t* reg_32 { reinterpret_cast<uint32_t*>(0x40020020) };

....

}

```

Now we've set up the pointer we can access the register indirectly through the pointer.

```

#include <cstdint>

using std::uint8_t;

using std::uint16_t;

using std::uint32_t;

int main()

{

uint8_t* reg_8 { reinterpret_cast<uint8_t*>(0x40020000) };

uint16_t* reg_16 { reinterpret_cast<uint16_t*>(0x40020010) };

uint32_t* reg_32 { reinterpret_cast<uint32_t*>(0x40020020) };

uint8_t value { };

value = *byte_reg; // Read

*byte_reg = 0; // Write

}

```

Since our hardware registers are at fixed locations in memory (and should never change!) we can improve the optimisation capacity of the compiler by making the pointers constants.

```

#include <cstdint>

using std::uint8_t:

using std::uint16_t:

using std::uint32_t:

int main()

{

uint8_t* const reg_8 { reinterpret_cast<uint8_t*>(0x40020000) }:

uint16_t* const reg_16 { reinterpret_cast<uint16_t*>(0x40020010) }:

uint32_t* const reg_32 { reinterpret_cast<uint32_t*>(0x40020020) }:

uint8_t value { }:

value = *byte_reg: // Read

*byte_reg = 0: // Write: also OK. Register is not constant

}

```

Remember, the const refers to the pointer, not the object being addressed (the register)

(It might seem compelling at this point to consider making the pointers a constexpr. After all, the pointer is fixed and can never change. However, the C++ standard explicitly prohibits the results of reinterpret\_cast in constant-expressions. See following link for more details - <a href="http://stackoverflow.com/questions/10369606/constexpr-pointer-value">http://stackoverflow.com/questions/10369606/constexpr-pointer-value</a>)

#### **Registers and side-effects**

One of the defining features of hardware registers is their value is dictated by the (current) state of the hardware; and not necessarily by the actions of the program. This means, for example:

- A write to a hardware register, followed by a read may not yield the same value. This is often true for write-only registers

- Two sequential reads from a register may yield different results

We could therefore declare any access to a hardware register – read or write – could yield a sideeffect.

However, the compiler can only reason about objects declared within the program. It will base all its optimisations on the code that is presented. For example:

```

int main()

{

uint8_t* const ctrl { reinterpret_cast<uint8_t*>(0x40020000) };

uint8_t* const cfg { reinterpret_cast<uint8_t*>(0x40020001) };

uint8_t* const data { reinterpret_cast<uint8_t*>(0x40020002) };

while(*data == 0)

{

// Wait for data to arrive...

}

}

```

The code above could fail at run-time; particularly at higher optimisation levels.

From the compiler's perspective there is no code to modify the object referenced by data. Therefore, the compiler is free to optimise out the (apparently) redundant reads and simply read **\*data** before the loop.

Similarly, the compiler is likely to optimise redundant writes; for example:

```

int main()

{

uint8_t* const ctrl { reinterpret_cast<uint8_t*>(0x40020000) };

uint8_t* const cfg { reinterpret_cast<uint8_t*>(0x40020001) };

uint8_t* const data { reinterpret_cast<uint8_t*>(0x40020002) };

*ctrl = 1; // Enter configuration mode

*cfg = 3; // Configure the device

*ctrl = 0; // Enter operational mode.

}

```

It is likely that the first write to \*ctrI will be optimised away, since there is no read of \*ctrI before the second write.

We have to inform the compiler that the object we are referencing via the pointer is a special case and therefore any optimisations (removing redundant reads / writes; or re-orderings) must be disabled for this object. Enter the *volatile* qualifier:

```

int main()

{

volatile uint8_t* const ctrl { reinterpret_cast<uint8_t*>(0x40020000) };

volatile uint8_t* const cfg { reinterpret_cast<uint8_t*>(0x40020001) };

volatile uint8_t* const data { reinterpret_cast<uint8_t*>(0x40020002) };

*ctrl = 1; // Redundant writes not optimised-out.

*cfg = 3;

*ctrl = 0;

...

while(*data == 0) { // Redundant reads not optimised-out

// Wait for data...

}

}

```

Unless you have a very good reason not to, all hardware-access pointers should be marked as volatile.

We've now established the basic idiom for accessing hardware via pointers.

#### An aside: decluttering code

Our pointer declarations are starting to look a bit verbose. We can use auto type-deduction to make our code cleaner:

```

int main()

{

auto const ctrl { reinterpret_cast<volatile uint8_t*>(0x40020000) }:

auto const cfg { reinterpret_cast<volatile uint8_t*>(0x40020001) }:

auto const data { reinterpret_cast<volatile uint8_t*>(0x40020002) }:

*ctrl = 1:

*cfg = 3:

*ctrl = 0:

while(*data == 0) {

// Wait for data...

}

}

```

}

There are a few things to note in this new code:

Since auto uses the type of the initialiser to determine the type of the object, we must change the type of the reinterpret\_cast<> to a volatile uint8\_t\*.

The const qualifier is applied *after* type-deduction and applies to the deduced type. So in this case our pointers become

```

volatile uint8_t* const ctrl;

volatile uint8_t* const cfg;

volatile uint8_t* const data;

```

Although our idiom is explicit (and for that reason, preferred) all the pointer dereferencing can make code less-than-clean to read.

As a C programmer we might resort to the pre-processor to clean up the code:

```

// C programmer' s version

//

#define CTRL (*(volatile uint8_t*) 0x4002000)

#define CFG (*(volatile uint8_t*) 0x4002010)

#define DATA (*(volatile uint8_t*) 0x4002020)

int main(void)

{

CTRL = 1;

CFG = 3;

CTRL = 0;

while(DATA == 0) {

//...

}

}

```

The macros (CTRL, CFG, DATA) perform an inline cast of an integer to a pointer, then immediately dereference it to get an object. So any access to CTRL (for example) will be an indirect access to the address 0x4002000.

In C++ we can use references to achieve the same effect. The advantage of using references is that they will appear in the symbol table, making debugging easier.

```

// C++ programmer' s version

//

int main()

{

auto& ctrl { *reinterpret_cast<volatile uint8_t*>(0x40020000) }:

auto& cfg { *reinterpret_cast<volatile uint8_t*>(0x40020010) }:

auto& data { *reinterpret_cast<volatile uint8_t*>(0x40020020) }:

ctrl = 1:

cfg = 3;

ctrl = 0;

while(data == 0) {

//...

}

}

```

Notice the pointer dereference in the initialisers - we want references to objects, not pointers. Also notice you don't have to make references const. References cannot be 're-seated' so are effectively always const.

Although we'll look at this more later it's worth mentioning that both the pointer and reference versions shown will generate the same opcodes. The choice, then, becomes which is clearer to the reader (and maintainer) of the code. For the rest of this paper, I'm going to stick to the pointer version. From an explanation point of view it is more explicit that we are indirectly accessing the IO memory.

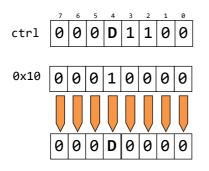

#### **Bit manipulation**

One of the distinguishing aspects of hardware manipulation code is that we are often dealing with variables on a bit-by-bit basis. There are a set of idiomatic operations we'll need to do regularly:

- Set a particular bit, or set of bits

- Clearing bit(s)

- Check to see if a bit is set or not

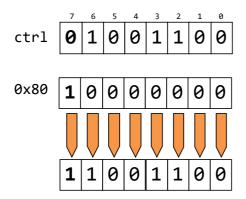

#### **Setting bits**

When setting individual bits a we have to leave all the bits we're not interested in unchanged. Therefore, a simple assignment is not adequate. We need bitwise OR:

```

int main()

{

auto const ctrl { reinterpret_cast<volatile uint8_t*>(0x40020000) };

auto const cfg { reinterpret_cast<volatile uint8_t*>(0x40020001) };

auto const data { reinterpret_cast<volatile uint8_t*>(0x40020002) };

*ctrl = *ctrl | Ob10000000; // Set bit 7

...

}

```

This code will set bit 7 of the ctrl register, leaving all others intact, since OR-ing with zero has no effect.

The above code explicitly shows the read-modify-write operation, although idiomatically programmers prefer the syntactic sugar of the OR-assignment operator.

\*ctrl |= 0b1000000;

Notice here we're using C++'s binary literal to specify the bits we want to set. Hard-coding bit values is fine for simple (8-bit) values but can become tedious – and error-prone – for multiple bits on larger words (For example, what about setting bits 17 and 23 on a 32-bit word?).

We could use hexadecimal:

\*ctrl |= 0x80

Or we can make use of the left-shift operator:

\*ctr| |= (1 << 7);

That is, put a 1 in the least-significant bit position then shift left 7 times. This will put the 1 in bit 7, the rightmost bits guaranteed to be zero.

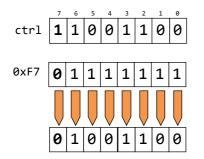

#### **Clearing a bit**

We (obviously?) can't use bitwise-OR to clear a bit since OR-ing with zero has no effect. When clearing a bit we need to set the offending bits to 0, whilst maintaining the state of all other bits. For this we use bitwise-AND

```

int main()

{

auto const ctrl { reinterpret_cast<volatile uint8_t*>(0x40020000) };

auto const cfg { reinterpret_cast<volatile uint8_t*>(0x40020001) };

auto const data { reinterpret_cast<volatile uint8_t*>(0x40020002) };

*ctrl |= (1 << 7); // Set bit 7

...

*ctrl &= 0b01111111; // Clear bit 7

...

}</pre>

```

To make the code more readable (for larger register sizes) we can again make use of the bitwise-NOT operator (~):

•ctrl &= ~0x80;

Or even:

\*ctr| &= ~(1 << 7);

#### Checking a bit

To check whether a bit is set, we again use bitwise-AND. An (bit) value AND-ed with 1 will retain its original value.

Note: the result will either be 0 if our target bit is not set, or *non-zero* if it is set. Therefore, always compare the result of the bitwise-AND operation to zero

#### **Read-only registers**

As the name suggests a read-only register cannot be written to. Writing to a read-only register is undefined.

Rather than rely on programmer diligence we can get the compiler to help us by marking our readonly registers as pointers-to-const:

```

int main()

{

auto const ro_reg { reintepret_cast<const volatile uint8_t*>(0x40020001) };

auto val = *ro_reg; // OK - Read allowed.

*ro_reg = 1; // FAIL - Write not allowed.

}

```

Hardware abstraction layers like CMSIS provide similar macros to define read-only and read-write registers

```

/* IO definitions (access restrictions to peripheral registers) */

/*CMSIS Global Defines

IO Type Qualifiers are used:

- to specify the access to peripheral variables.

- for automatic generation of peripheral register debug

information.

*/

#define __I volatile const /* Defines 'read only' permissions */

#define __O volatile /* Defines 'write only' permissions */

#define __I0 volatile /* Defines 'read/write' permissions */

```

#### Write-only registers

A write-only register can only be written to. The value read from a write-only register is undefined. They are likely to be junk, and no reflection of the actual state of the register.

Therefore, the code idioms I've shown above should not be used with write-only registers. In fact, they could even be dangerous. Writing back a (modified) version of a junk value (from a read) could unintentionally enable bits in the register!

When accessing write-only registers only ever use the assignment operator (=)

```

int main()

{

// Can we enforce write-only?

//

auto const wo_reg { reintepret_cast<volatile uint8_t*>(0x40020002) }:

auto val = *wo_reg: // Will compile, but invalid

*wo_reg = 0x55: // Never use |= to set bits

}

```

Unfortunately, unlike read-only registers there's no way with pointers of ensuring you never read the pointer (you can always read an object in C++). You are reliant on the programmer applying due diligence. (Notice in the CMSIS code above the definition for write-only is the same as for read-write!)

We will explore how C++ can help us enforce register read- and write- characteristics later in this document.

## General-Purpose Input-Ouput (GPIO)

#### "Hello World" for embedded programmers

Although this paper is about general principles it's always nice to have a concrete example to work with. In this case I'm aiming my code at an STM32F4 Discovery board based on an ARM Cortex M4 processor.

The classic "Hello World" for embedded programmers is to flash one of the LEDs on the target board.

On the STM Discovery board there are four LEDs. The LEDs are controlled via one of the General Purpose Input-Output (GPIO) ports on the microcontroller.

#### **GPIO basics**

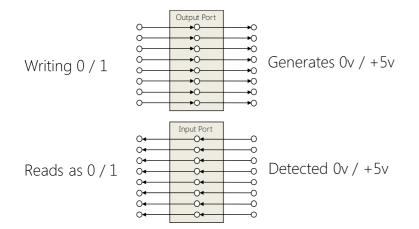

Central to modern microcontrollers is the ability to perform general purpose I/O (GPIO). External pins can then be connected to physical hardware to sense or control voltages.

Conceptually, we could imagine each pin being represented by a bit in a hardware register. For example, we could have a output register where writing 1/0 to a bit would cause a 5V/0V output to be produced on the physical pin. Similarly, applying 5V/0V to an input pin would cause the appropriate bit in the input register to signal 1/0.

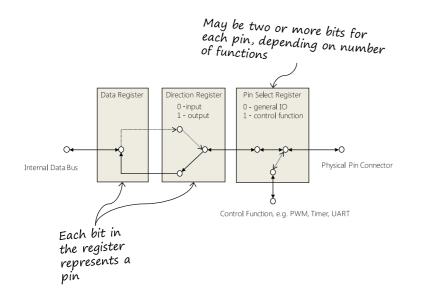

Such a mechanism would lead to a profusion of pins, and be very inflexible – there would always be a fixed number of input and output pins. In most real world microcontrollers each physical pin can be configured for a variety of uses. Usually the I/O pins are multiplexed so they can not only act as either inputs or outputs, but also perform alternative operations (e.g. transmit pin for RS232).

This means for a typical GPIO port there are multiple hardware registers involved in its use:

- A function-select register to specify whether the pin is being used for GPIO or some other function

- A direction register to specify whether the pin is an input or output

- One (or more) data registers for reading / writing data

The number of, and operation of, the GPIO registers is hardware-specific and will vary from manufacturer to manufacturer; but they typically all have the same basic principles.

#### STM32F407VG GPIO

The STM32F407VG microcontroller has 9 identical GPIO ports, labelled A - I. Each GPIO port is highly configurable and each output pin can have several functions (usually digital input and output, analog; and up to 16 alternative functions)

Each peripheral on the STM32F407 is clock-gated. The clock signal does not reach the peripheral until we tell it to do so by way of setting a bit in a register (known as the Reset and Clock Control, or RCC, register). By default, clock signals never reach peripherals that are not in use, thus saving power.

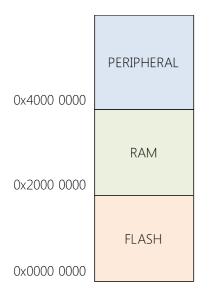

#### The memory map

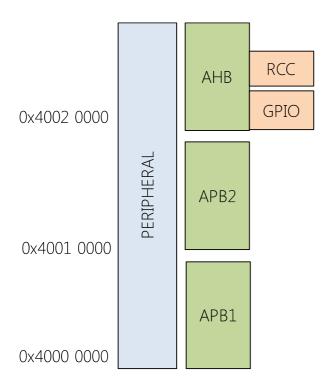

One of the very convenient features of the ARM Cortex M architecture is that the memory map is well-defined. The basic memory map looks like this:

The STM32F407VG has three peripheral buses

- 1 Advanced High-Performance Bus (AHB)

- 2 Advanced Peripheral Bus (APB)

All the GPIO ports are on the Advanced High Performance bus. The addresses of the ports are shown in the table below

| Port | Base Address |

|------|--------------|

| A    | 0x4002 0000  |

| В    | 0x4002 0400  |

| С    | 0x4002 0800  |

| D    | 0x4002 0C00  |

| E    | 0x4002 1000  |

| F    | 0x4002 1400  |

| G    | 0x4002 1800  |

| Н    | 0x4002 1C00  |

| I    | 0x4002 2000  |

#### The GPIO hardware registers

There are 10 configuration / data registers for each GPIO port but for our purposes we only need to consider three -

- the Mode register, to configure

- the Input Data register

- the Output Data register.

|                                                    | offset |

|----------------------------------------------------|--------|

| Port mode register (GPIOx_MODER)                   | 0x00   |

| Port output type register (GPIOx_OTYPER)           | 0x04   |

| Port output speed register (GPIOx_OSPEEDR)         | 0x08   |

| Port pull-up/pull-down register (GPIOx_PUPDR)      | 0x0C   |

| Port input data register (GPIOx_IDR)               | 0x10   |

| Port output data register (GPIOx_ODR)              | 0x14   |

| Port bit set/reset register (GPIOx_BSRR)           | 0x18   |

| Port configuration lock register (GPIOx_LCKR)      | 0x1C   |

| Port alternate function low register (GPIOx_AFRL)  | 0x20   |

| Port alternate function high register (GPIOx_AFRH) | 0x24   |

Notice that all registers are 32-bit (although in many cases not all 32 bits are used).

To keep the code simple we're going to do bare-minimum configuration and pretty much ignore good practices like error-checking, parameter validation, etc.

In a real-world system we would probably want to explicitly configure the output type, output speed and pull-up/pull-down settings for the port. The default settings for these registers are fine for this example, so to save space I'm going to ignore those registers. There are three steps to getting our "Hello World" flashing LED:

- Declare our hardware register pointers

- Enable the GPIO port clock

- Configure the port for output

- Flash the LED by turning the pin on/off

#### Declaring the hardware registers

The LEDs on the STM32F4-Discovery are all on GPIO port D; on pins 12 – 15. For this exercise we'll flash the blue LED (pin 15).

To add a (bare minimum) of flexibility I've declared the addresses of the hardware components as constant-expressions.

```

#include <cstdint>

using std::uint32_t;

constexpr auto RCC_addr { 0x40023830 };

constexpr auto GPI0_addr { 0x40020C00 };

auto const RCC_AHB1ENR { reinterpret_cast<uint32_t*>(RCC_addr) };

auto const GPI0_MODER { reinterpret_cast<volatile uint32_t*>(GPI0_addr + 0x00) };

auto const GPI0_IDR { reinterpret_cast<volatile uint32_t*>(GPI0_addr + 0x10) };

auto const GPI0_ODR { reinterpret_cast<volatile uint32_t*>(GPI0_addr + 0x14) };

int main()

{

// ...

}

```

#### **Enabling the GPIO port clock**

Each device on the AHB1 bus is enabled using a special configuration register, the AHB1 RCC Enable Register

| 31            | 30                      | 29          | 28                  | 27                 | 26                 | 25           | 24          | 23          | 22       | 21          | 20          | 19          | 18               | 17   | 16            |      |       |

|---------------|-------------------------|-------------|---------------------|--------------------|--------------------|--------------|-------------|-------------|----------|-------------|-------------|-------------|------------------|------|---------------|------|-------|

| Reser-<br>ved | OTGH<br>S<br>ULPIE<br>N | OTGH<br>SEN | ETHM<br>ACPTP<br>EN | ETHM<br>ACRXE<br>N | ETHM<br>ACTXE<br>N | ETHMA<br>CEN | Reserved -  |             | Reserved |             | DMA2E<br>N  | DMA1E<br>N  | CCMDAT<br>ARAMEN | Res. | BKPSR<br>AMEN | Rese | erved |

|               | rw                      | rw          | rw                  | rw                 | rw                 | rw           |             |             | rw       | rw          |             |             | rw               |      |               |      |       |

| 15            | 14                      | 13          | 12                  | 11                 | 10                 | 9            | 8           | 7           | 6        | 5           | 4           | 3           | 2                | 1    | 0             |      |       |

| Reserved      |                         | CRCE<br>N   | Reserved            |                    | GPIOIE<br>N        | GPIOH<br>EN  | GPIOG<br>EN | GPIOFE<br>N | GPIOEEN  | GPIOD<br>EN | GPIOC<br>EN | GPIO<br>BEN | GPIO<br>AEN      |      |               |      |       |

|               |                         | rw          |                     |                    |                    |              |             | rw          | rw       | rw          | rw          | rw          | rw               | rw   | rw            |      |       |

We could hard-code this value for our exercise (which would work just fine). As a generic solution it's worth noting that bits [13:10] of the port's address map onto the bit position in the RCC AHB1 Enable Register:

40020000 => 0b0100' 0000' 0010' 0010' 0000' 0000' 0000' 0000 => Port A 40020400 => 0b0100' 0000' 0000' 0010' 0000' 0100' 0000' 0000 => Port B 40020800 => 0b0100' 0000' 0000' 0010' 0000' 1000' 0000' 0000 => Port C 40020000 => 0b0100' 0000' 0000' 0010' 0000' 1100' 0000' 0000 => Port D Thus we can mask off those 4 bits of a port's address to work out which port number it is.

```

inline void enable_device(uint32_t address)

{

// The 4 bits [13:10] identify the

// port.

//

auto port_number = (address >> 10) & 0x0F;

*RCC_AHB1ENR |= (1 << port_number);

}</pre>

```

#### Configuring the port for output

To enable a pin for output we must configure its port's mode.

| 31    | 30       | 29    | 28       | 27    | 26       | 25             | 24       | 23          | 22       | 21          | 20       | 19          | 18           | 17          | 16          |  |

|-------|----------|-------|----------|-------|----------|----------------|----------|-------------|----------|-------------|----------|-------------|--------------|-------------|-------------|--|

| MODEF | R15[1:0] | MODEF | R14[1:0] | MODEF | R13[1:0] | MODEF          | R12[1:0] | MODEF       | R11[1:0] | MODEF       | R10[1:0] | MODE        | ODER9[1:0] M |             | MODER8[1:0] |  |

| rw    | rw       | rw    | rw       | rw    | rw       | rw             | rw       | rw          | rw       | rw          | rw       | rw          | rw           | rw          | rw          |  |

| 15    | 14       | 13    | 12       | 11    | 10       | 9              | 8        | 7           | 6        | 5           | 4        | 3           | 2            | 1           | 0           |  |

| MODE  | R7[1:0]  | MODE  | R6[1:0]  | MODE  | R5[1:0]  | )] MODER4[1:0] |          | MODER3[1:0] |          | MODER2[1:0] |          | MODER1[1:0] |              | MODER0[1:0] |             |  |

| rw    | rw       | rw    | rw       | rw    | rw       | rw             | rw       | rw          | rw       | rw          | rw       | rw          | rw           | rw          | rw          |  |

Each pin has four modes of operation, thus requiring two configuration bits per pin:

- 00 Input

- 01 Output

- 10 Alternative function (configured via the AFRH and AFRL registers)

- 11 Analogue

We can generalise this into a simple function. Note that, because there are two configuration bits per pin, we must multiply the pin number by two to get the correct offset into the register.

```

inline void set_as_output(unsigned int pin_num)

{

*GPI0_MODER |= (Ob01 << (pin_num * 2));

}</pre>

```

#### **Flashing the LED**

Flashing the LED requires turning on / off the appropriate pin. A pair of functions will suffice. Notice, unlike the mode configuration, controlling a pin only requires one bit (on/off).

```

inline void turn_on_pin(unsigned int pin_num)

{

*GPI0_0DR |= (1 << pin_num);

}

inline void turn_off_pin(unsigned int pin_num)

{

*GPI0_0DR &= ~(1 << pin_num);

}</pre>

```

Finally, our main () function puts all this together:

```

int main()

{

enable_device(GPI0_addr);

set_as_output(15); // Pin 15 is the blue LED

while(true) {

turn_on_pin(15);

sleep(1000); // Some generic busy-wait...

turn_off_pin(15);

sleep(1000);

}

}

```

#### Under the hood

Let's have a quick look at the generated assembler for this code. For this example I'm using the ARM gcc compiler toolchain, generating Thumb2 instructions. I've turned the optimiser off (00).

I don't want to dwell on this code much here. Since this is pretty much the minimum code we could write to get our "Hello World" working it's a useful benchmark for any code we generate later.

In the code below I've removed the opcodes for the call to the generic sleep() function since they aren't really relevant to what we're examining.

```

; main()

08000d14:

ldr

r2, [pc, #36]

; r2 = 0x40023830 <RCC_AHB1ENR>

08000d16:

ldr

r3, [r2, #0]

; r3 = *r2

08000d18:

orr.w

r3, r3, #8

; r3 = r3 | 0x08

08000d1c:

str

r3, [r2, #0]

; *r2 = r3

08000d1c: str r3, [r2, #0]

; *GPIO MODER |= (ObO1 << (pin num * 2));

08000d1e: Idr r2, [pc, #32] ; r2 = 0x40020C00 <GPI0_MODER>

08000d20: Idr r3, [r2, #0] ; r3 = *r2

08000d22: orr.w r3, r3, #1073741824 ; r3 = r3 | 0x4000000

08000d26: str r3, [r2, #0] ; *r2 = r3

; while(true) {

; *GPI0_ODR |= (1 << pin_num);

loop:

08000d28:

Idr

r2, [pc, #24]

; r2 = 0x40020C14 <GPI0_0DR>

08000d2a:

Idr

r3, [r2, #0]

; r3 = *r2

08000d2c:

orr.w

r3, r3, #32768

; r3 = r3 | 0x8000

08000d30:

str

r3, [r2, #0]

; *r2 = r3

; *GPIO_ODR &= ~(1 << pin_num);

08000d32: Idr r3, [r2, #0] : r3 = *r2 <GPI0_ODR>

08000d34: bic.w r3, r3, #32768 : r3 = r3 & ~0x8000

08000d38: str r3, [r2, #0]

; *r2 = r3

; }

08000d3a: b.n 0x8000d28

; goto loop

; Register addresses:

08000d3c: dcd 1073887280

; 0x40023830

; 0x4002000

; 0x40020000

08000d40: dcd 1073875968

08000d44: dcd 1073875988

; 0x40020C14

```

## An object-based approach

Hardware devices lend themselves nicely to an object-based approach. Each hardware device has an equivalent software object for accessing it; there is a one-to-one mapping between devices and objects.

Encapsulating device access within a class gives us a number of other benefits:

- The member functions decouple the actual access from the application. We can easier separate interface (API) from implementation

- Constructors can be used to initialise the device, removing the need for the client to explicitly do so. Destructors can be used to place the device back into a 'safe' state.

- We can support multiple devices.

- We can use specialisation (inheritance) to provide 'families' of devices.

#### Interface design

Before we look at implementation it's worth taking some time to explore our client interface (API). Firstly, there's no such thing as a 'perfect' API. All interface designs will make assumptions and compromises; design is the act of balancing these things.

We (generally) want to provide an interface that is simpler than the underlying implementation (otherwise, what would be the point?). This means not only encapsulating implementation details, but also restricting the allowable behaviour of the device. As a rule-of-thumb, the more fine-grained control you grant clients the less portable your API is. That is, allowing fine-grain control generally requires exposing more of the underlying implementation, which is the non-portable part.

For our GPIO class we have a couple of options:

#### **Bitmask-based member functions**

In this interface design the client provides bit masks that specify which bits are to be set / cleared. This interface allows multiple bits to be set / cleared in one call.

Clients can perform bitwise operations on the GPIO device as if it were a single abstract memory location; the fact that there are multiple registers being manipulated is hidden from the client.

```

class GPI0 {

public:

void direction(std::uint32_t bitmask);

GPI0& operator=(std::uint32_t bitmask);

operator uint32_t();

GPI0& operator &= (std::uint32_t bitmask);

GPI0& operator |= (std::uint32_t bitmask);

};

```

From a client perspective using the GPIO class looks a lot like using a pointer-based technique.

```

int main()

{

// Create a GPIO object, port_D (see later

// for a discussion on object construction)

port_D. direction(1 << 15);

while(true) {

port_D |= (1 << 15);

sleep(1000);

port_D &= ~(1 << 15);

sleep(1000);

}

}</pre>

```

#### **Pin-based member functions**

Here we are restricting clients to manipulating one GPIO pin at a time. We could perhaps restrict clients even more by using an enumeration for the pins. For example:

```

class GP10 {

public:

enum Pin {

Pin00, Pin01, Pin02, Pin03,

Pin04, Pin05, Pin06, Pin07,

Pin08, Pin09, Pin10, Pin11,

Pin12, Pin13, Pin14, Pin15,

};

void set_as_output(Pin pin);

void set_as_input (Pin pin);

void set_pin (Pin pin);

void clear_pin(Pin pin);

bool is_set (Pin pin);

};

```

This interface design removes the need for bit calculations from the client.

```

int main()

{

// Create the GPIO object, port_D...

port_D.set_as_output(Pin15);

while(true) {

port_D.set(Pin15);

sleep(1000);

port_D.clear(Pin15);

sleep(1000);

}

}

```

#### The Pin class

This idea could be taken further by defining a GPIO Pin class that represents a single pin on a port.

class Pin { public:

```

Pin(Port port, unsigned int number);

void set();

void clear();

bool is_set();

Pin& operator=(unsigned int val);

operator unsigned int();

};

```

This is the most 'abstract' API, treating each physical pin as a one-bit integer.

```

int main()

{

// Create a Pin object, blue_LED...

blue_LED.direction(Pin::OUTPUT);

while(true) {

blue_LED = 1;

sleep(1000);

blue_LED = 0;

sleep(1000);

}

}

```

#### **Choosing an interface**

Firstly, there's no such thing as a 'perfect' API. All interface designs will make assumptions and compromises; design is the act of balancing these things.

As a rule-of-thumb, the more fine-grained control you grant clients the less portable your API is. That is, allowing fine-grain control generally requires exposing more of the underlying implementation, which is the non-portable part.

For individual bit-manipulation a pin-based (or Pin class) interface is generally easier to use. However, if your hardware requires multiple bits to be set a bitmask-based interface is more useful. Often, you can't know in advance which mechanism will be most valuable to the client so you provide a 'combination' interface; for example adding functions for both pin-based and bitmask-based calls.

For this article I'm going to use the pin-based GPIO API since the member function implementations are very close to the code we have seen in previous articles. I'll leave it as a perennial 'exercise for the reader' to implement the other APIs.

#### **Construction and destruction**

There are two problems we need to solve with our GPIO class constructor

- Identifying a unique hardware port

- Configuring the hardware for use

GPIO objects map explicitly (and, ideally, exclusively) onto a single hardware device. We could use the hardware address for the device. This is certainly unique but requires the client correctly remember a set of arcane, and target-specific, numbers in order to use the device.

Better, perhaps, would be to use an abstract identifier – an enumeration – for the device.

```

namespace STM32F407 {

enum device {

GPIO_A, GPIO_B, GPIO_C,

GPIO_D, GPIO_E, GPIO_F,

```

```

GPIO_G, GPIO_H, GPIO_I

};

```

I'm putting device-specific elements (there will be more, shortly) in a namespace to separate it.

We can now use this enumeration as a constructor parameter:

```

class GPI0 {

public:

explicit GPI0(STM32F407::device id);

// Other API...

};

```

Note the constructor is marked explicit. This is to stop implicit conversion of (random!) integers to GPIO objects.

Inside the GPIO constructor, we need to enable the clock to the particular GPIO hardware device. A simple function will suffice for this.

```

namespace STM32F407 {

enum device {

GPI0_A, GPI0_B, GPI0_C,

GPI0_D, GPI0_E, GPI0_F,

GPI0_G, GPI0_H, GPI0_I

};

constexpr std::uint32_t periph_base { 0x40020000 }:

inline void enable_device(device dev)

{

auto const enable_reg { reinterpret_cast<volatile std::uint32_t*>(periph_base + 0x3830) }:

*enable_reg |= (1 << dev);

}

}</pre>

```

The call to this function can be made within the GPIO constructor.

```

GPI0::GP10(STM32F407::device dev)

{

STM32F407::enable_device(dev);

}

```

The destructor on the GPIO could do nothing (the default); or it place the device back into a safe / quiescent state. In our system one option would be to disable the clock to the hardware device. A complementary function to the enable\_device() function above could be simply written. Note, however, the GPIO class has to store its device ID as a member in order to call the function.

```

class GP10 {

public:

explicit GP10(STM32F407::device dev);

~GP10();

// Other API...

private:

STM32F407::device ID;

};

GP10::GP10(STM32F407::device dev) :

ID { dev }

{

STM32F407::enable_device(ID);

}

```

```

GP10::~GP10()

{

STM32F407::disable_device(ID);

}

```

#### Copy and move policy

Since there is a one-to-one mapping between objects and the physical hardware we have to think carefully about copying (and, by extension, moving) objects.

What does it mean to 'copy' a hardware device? It could mean:

- Two GPIO objects both refer to the same hardware device (the default copy behaviour)

- All the configuration of one hardware port is copied to another

- All the configuration settings and current output values are copied

None of these options is particularly desirable (or safe), so our 'best' option is to disable copying; and moving, for similar reasons.

```

class GPI0 {

public:

explicit GPI0(STM32F407::device dev);

~GPI0();

// Copy and move policy

//

GPI0(const GPI0&) = delete;

GPI0(GPI0&) = delete;

GPI0& operator=(const GPI0&) = delete;

GPI0& operator=(GPI0&) = delete;

};

```

#### When things go wrong

A crucial part of a class's interface design is what happens when things go wrong. That is, what is the mechanism by which you report success / failure on an object's behaviour. Within an operation there are generally two places you will apply error checking

- Pre-condition validation The input parameters to the operation are not acceptable

- Post-condition validation The resulting behaviour of the operation is outside some acceptable bounds

When an error condition occurs you have four options:

- Do nothing

- Return an error

- Throw an exception

- Terminate

Each of these options has a different level of consequence.

#### Do nothing

Silently ignoring failures when manipulating hardware could be potentially catastrophic to your system. However, if it is known that the exception does not affect system operation it can be safely ignored without consequence. In other cases the error condition may be transient (for example, during a system mode change) and it is understood that the error condition will not persist.

#### **Return an error**

Returning an error code gives a mechanism for our hardware manipulation code to report back its status.

The design of a function's interface can affect the explicitness of error handling. For example, consider the two operations on our GPIO class

```

class GPI0 {

public:

error_code set_pin(Pin pin);

void clear_pin(Pin pin, error_code& err);

};

```

For set\_pin() the error code, being the return value from the function, can be implicitly ignored. This gives the potential to miss error conditions, which could lead to failures, hazardous system conditions and all sorts of undesirable consequences.

C++17 gives us a mechanism to prevent the ignoring of error return codes. Marking our function with the [[nodiscard]] attribute encourages the compiler to emit a warning if the return value is not used.

```

class GPI0 {

public:

[[nodiscard]] error_code set_pin(Pin pin);

...

};

int main()

{

GPI0 port_D { STM32F407::GPI0_D };

port_D.set_pin(GPI0::Pin15); // WARNING: error_code ignored

}

```

For clear\_pin() the error condition, passed as an input-output parameter, must be supplied by the client (caller) and the compiler will give a warning if the error code is not subsequently read; unless it is explicitly 'ignored' by the caller.

Up to C++17 to ignore the unused error\_code we would explicitly cast it to void to prevent a compiler warning. From C++17 we can hint to the compiler that we may not be checking the error\_code.

Notice, in the case of operator overloads there is no way of returning error codes (without breaking the semantics of the operator overload).

#### **Global error objects**

An alternative to error codes, then, is to use some global error condition object that can be updated and checked by clients.

Use of global error objects (and global objects in general) is frowned upon in modern programming, so we'll say no more of it here.

#### Throw an exception

Throwing an exception provides a couple of benefits over error codes. We can exploit the exception handling mechanism of the language to route error conditions to where they can be most appropriately handled. Client code becomes more explicit, separating behaviour code from failure code. Also, the behavioural API does not need to be cluttered with error handling

However, the cost of this is an increase in program size; and exception handling is non-deterministic and slow (when exceptions are thrown; there should be no little, or no, run-time cost if exceptions are not thrown). For this reason many embedded systems explicitly disable exception handling.

More subtly, but arguably far more important, exception handling strategies must be built into your code from the ground up. Simply adding ad-hoc exceptions to pre-existing code is likely to wreak havoc on the performance, maintainability and extensibility of your system.

#### Terminate

This is, of course, the extreme option. Use assert-like code to terminate code on error conditions. In application code, terminate-on-error will likely lead to code that is frustratingly cumbersome for clients to use. However, hardware is far more pernickety. There is little tolerance or error – the hardware is either working or it isn't. Terminating code is a 'reasonable' option with hardware manipulation; particularly with respect to pre-condition validation.

### Implementation

#### Implementation options

There are three mainstream approaches to hardware access available to us:

- Nested pointers / references

- Pointer offsets

- Structure overlay

Nested pointers are the simplest, and probably most common, approach but can have some memory overhead costs. Pointer offsets and structure overlay are more memory-efficient but can have some shortcomings if not implemented carefully.

#### **Nested pointers / references**

Nested pointers, as the name suggests, involves storing a pointer to each hardware register as a private member within the class.

```

class GPIO {

public:

explicit GPIO(STM32F407::device dev);

~GPIO();

// Copy and move policy...

// Behavioural API...

private:

STM32F407::device ID;

volatile std::uint32_t* const mode;

volatile std∷uint32_t* const type;

volatile std::uint32_t* const speed;

volatile std::uint32_t* const pull_up_down;

volatile std::uint32_t* const input_data;

volatile std::uint32_t* const output_data;

volatile std::uint32_t* const set_reset;

volatile std∷uint32_t* const lock;

volatile std::uint32_t* const alt_fn_low;

volatile std::uint32_t* const alt_fn_high;

};

```

Note, the pointers are declared as const. This means the default copy constructor and assignment operator are not available; but since we declared these operations as deleted this does not affect the design of this class.

Since the pointers are constants they must be initialised in the GPIO constructor. At the moment, though, we don't have an address to 'force' into the pointers; only an enumeration identifying the device.

Luckily, in our case there is a direct mapping between the device's ID and its address in memory. We can construct a simple conversion function to do the mapping.

```

namespace STM32F407 {

inline constexpr uint32_t device_address(device dev)

{

return peripheral_base + (dev << 10);

}

}</pre>

```

}

We can use this function when constructing the class:

```

using std∷uint32_t;

using STM32F407::device_address;

GP10::GP10(STM32F407::device dev) :

ID

{ dev }.

NOTE: This is NOT pointer

//

//

arithmetic!

//

{ reinterpret_cast<uint32_t*>(device_address(dev) + 0x00) },

mode

{ reinterpret_cast\langle uint32_t* \rangle (device_address(dev) + 0x04) },

type

{ reinterpret_cast<uint32_t*>(device_address(dev) + 0x08) },

speed

pull_up_down { reinterpret_cast<uint32_t*>(device_address(dev) + 0x0C) },

input_data { reinterpret_cast<uint32_t*>(device_address(dev) + 0x10) },

\label{eq:control} output_data ~ \{ \mbox{ reinterpret_cast} (\mbox{dist} 2_t * > (\mbox{device_address} (\mbox{dev}) \ + \ 0x14) \ \},

set_reset { reinterpret_cast<uint32_t*>(device_address(dev) + 0x18) },

lock { reinterpret_cast<uint32_t*>(device_address(dev) + 0x10) },

alt_fn_low { reinterpret_cast<uint32_t*>(device_address(dev) + 0x20) },

alt_fn_high { reinterpret_cast<uint32_t*>(device_address(dev) + 0x24) }

STM32F407::enable_device(ID);

}

```

A small point to note here: Programmers unused to the above notation often make the mistake of thinking the addition in the pointer initialisers is actually pointer arithmetic. The addition is done as (unsigned) integers, *then* cast to a pointer type.

The behavioural member functions of the class can now be implemented in much the same way as we have done previously; for example:

```

void GPIO::set_pin(GPIO::Pin pin)

{

*output_data |= (1 << pin);

}

void GPIO::clear_pin(GPIO::Pin pin)

{

*output_data &= ~(1 << pin);

}</pre>

```

The client code is very clean.

```

int main()

{

GPI0 port_d { STM32F407::GPI0_D };

port_d.set_as_output(GPI0::Pin15);

while(true) {

port_d.set_pin(GPI0::Pin15);

sleep(1000);

port_d.clear_pin(GPI0::Pin15);

sleep(1000);

}

}

```

From a performance perspective the code looks very similar to our earlier example.

```

; main() {

08000d78: push {|r}

08000d7a: sub sp, #52

; Allocate memory for GPIO

; GPIO port_d { STM32F407::GPI0_D };

08000d7c: add r0, sp, #4

; r0 = &port_d

08000d7e: movs r1, #3 ; r1 = STM32F407::GPI0_D

08000d80: b1 0x8000cf8 ; GPI0::GPI0()

; port_d.set_as_output(GPIO::Pin15);

08000d84: Idr r2, [sp, #8] ; r2 = mode

08000d86: Idr r3, [r2, #0] ; r3 = *r2;

08000d88: \quad \text{orr.w} \quad \text{r3, r3, } \#1073741824 \quad ; \text{ r3 } = \text{r3} \ | \ 0x40000000

08000d8c: str r3, [r2, #0] ; *r2 = r3

; while (true) {

; port_d.set_pin(GPIO::Pin15);

loop:

08000d8e:

Idr

r2, [sp, #28]

; r2 = output_data

08000d90:

Idr

r3, [r2, #0]

; r3 = *r2

08000d92:

orr.w

r3, r3, #32768

; r3 = r3 | 0x8000

08000d96:

str

r3, [r2, #0]

; *r2 = r3

; port_d.clear_pin(GPIO::Pin15);

.08000d98:Idrr2, [sp. #28]; r2 = output_data08000d9a:Idrr3, [r2, #0]; r3 = *r208000d9c:bic.wr3, r3, #32768; r3 = r3 & ~0x800008000da0:strr3, [r2, #0]; *r2 = r3

08000da2: b.n 0x8000d8e

; goto loop

; }

```

One of the drawbacks of the nested pointer approach is the amount of memory required for each GPIO object. In the case of our example each 32-bit hardware register has a software analogue in the form of a 32-bit pointer. This seems reasonable. However, if our hardware consisted of 8-bit registers our software object would be four times the size the hardware device it accessed.

Of course, we could omit some of these pointers if we are not exposing the behaviour they allow (for example, only using the default output type and speed).

#### **Pointer offsets**

An alternative, and more memory-efficient, implementation can exploit the fact that the hardware registers are always at fixed offsets from some base address. We can store a single pointer and use pointer arithmetic to access individual registers. The code can be made more readable by using an enumeration.

```

class GPIO {

public:

explicit GPI0(STM32F407::device dev);

~GPIO();

// Copy and move policy...

// Behavioural API...

private:

STM32F407::device ID;

volatile uint32_t* const registers; // Base address

enum Offset {

// Offsets

mode,

type.

speed,

pull_up_down,

input_data,

output data.

set_reset,

lock,

alt_fn_low,

alt_fn_high

};

};

```

The constructor is commensurately simpler, also.

```

GPI0::GPI0(STM32F407::device dev) :

ID { dev },

registers { reinterpret_cast<uint32_t*>(device_address(dev)) }

{

STM32F407::enable_device(ID);

}

```

In order to access individual registers we now have to perform pointer arithmetic on the base address.

```

void GPIO::set_pin(GPIO::Pin pin)

{

*(registers + output_data) |= (1 << pin);

}

void GPIO::clear_pin(GPIO::Pin pin)

{

*(registers + output_data) &= ~(1 << pin);

}</pre>

```

The readability of the code is starting to suffer now (to say the least). We can make an improvement by exploiting the relationship between pointer arithmetic and the index operator

```

void GPI0::set_pin(GPI0::Pin pin)

{

registers[output_data] |= (1 << pin);

}

void GPI0::clear_pin(GPI0::Pin pin)

{</pre>

```

registers[output\_data] &= ~(1 << pin);

}</pre>

We've made a potentially significant improvement in our memory-efficiency now: irrespective of the number of registers the size of the object remains the same – a single pointer (plus any additional management data).

Run-time performance is not affected, either:

```

; main() {

08000d44: push {|r}

08000d46: sub sp, #12

; Allocate memory for port d

; GPI0 port_d { STM32F407::GPI0_D };

08000d48: mov r0, sp

08000d4a: movs r1, #3

08000d4c: b1 0x8000cf8

: r0 = \& port d

; r1 = STM32F407::GPI0_D

; GPI0::GPI0()

; port_d.set_as_output(GPIO::Pin15);

; r2 = registers

08000d50: Idr r2, [sp, #4]

08000d52:

Idr

r3, [r2, #0]

; r3 = registers->mode

08000d54:

orr.w

r3, r3, #1073741824

; r3 = r3 | 0x4000000

08000d58:

str

r3, [r2, #0]

; registers->mode = r3

; while(true) {

; port_d.set_pin(GPIO::Pin15);

loop:

08000d5a: Idr r3, [sp, #4]

08000d5c: Idr r2, [r3, #20]

; r3 = registers

U8000d5a:

Idr

r3, [sp, #4]

: r3 = registers

08000d5c:

Idr

r2, [r3, #20]

: r2 = registers->c

08000d5e:

orr.w

r2, r2, #32768

: r2 = r2 | 0x8000

; r2 = registers->output_data

08000d62: str r2, [r3, #20]

; registers->output_data = r2

; port_d.clear_pin(GPIO::Pin15);

08000d64: Idr

r2, [r3, #20]

; r2 = registers->output_data

08000d66: bic.w r2, r2, #32768

08000d6a: str r2, [r3, #20]

; r2 = r2 \& ~0x8000

; registers->output_data = r2

08000d6c: b.n 0x8000d5a

; goto loop

08000d6e: nop

; }

```

#### Structure overlay

The main limitation of the pointer offset implementation is that all registers must be the same size, and/or any offsets between registers (if they are not contiguous) must be the some multiple of the register size. This is because the pointer offset implementation basically treats the hardware memory as an array.

In our example the pointer offset implementation is a viable option; but that is not always the case. It is possible (although less likely these days) that you have different-sized registers, or registers at odd offsets. For these situations a structure overlay is a good option.

Structure overlay make uses of the fact that the type of a pointer defines not only how much memory to read but also how to interpret it. Until now we have been using pointers to scalar types – unsigned integers. There is nothing to stop us declaring a pointer to a user-defined type, with multiple members (in other words, a class or structure)

If we can define a structure that matches our hardware register layout we can 'overlay' this structure on memory by declaring a pointer to the struct type and 'forcing' an address into the pointer. **A big word of warning here:**

By default, the compiler is free to insert padding into a structure's layout to word-align the members for more efficient access. This can mean that actual structure has a different size and member offsets to the structure you declared. This will be invisible from the code; and a pain to debug.

When using structures for hardware overlay ALWAYS pack the structures (that is, force the compiler to remove any padding). Unless you can guarantee that your structure will never be padded.

Unfortunately, structure packing is not part of the C++ standard so the packing instruction is always compiler-specific.

In our example our registers are all 32-bit and contiguous in memory; therefore we can be comfortable that we will have no padding issues.

Here's the class declaration

```

class GPIO {

public:

explicit GPIO(STM32F407::device dev);

~GPIO();

// Copy and move policy...

// Behavioural API...

private:

STM32F407::device ID;

// Overlay structure

11

struct Registers {

std∷uint32_t mode;

std∷uint32_t type;

std∷uint32 t speed;

std::uint32_t pull_up_down;

std∷uint32_t input_data;

std::uint32_t output_data;

std∷uint32_t set_reset;

std∷uint32_t lock;

std∷uint32_t alt_fn_low;

std∷uint32_t alt_fn_high;

};

volatile Registers* const registers;

};

```

Notice the struct declaration is a private declaration within the GPIO class. Since this is a declaration it does not add to the size of a GPIO object.

The constructor has to change. Note we're now casting our address to a pointer-to-structure.

```

GPI0::GPI0(STM32F407::device dev) :

ID { dev },

registers { reinterpret_cast<Registers*>(device_address(dev)) }

{

STM32F407::enable_device(ID);

}

```

In the member functions we can make use of the pointer-to-member operator. The compiler will automatically calculate the member offsets from the base address

```

void GPI0::set_pin(GPI0::Pin pin)

{

registers->output_data |= (1 << pin);

}

void GPI0::clear_pin(GPI0::Pin pin)

{

registers->output_data &= ~(1 << pin);

}</pre>

```

From a memory perspective, the structure overlay implementation has the same footprint as the pointer-offset implementation.

From a code-performance perspective?

```

; main() {

08000d44: push {|r}

08000d46: sub sp, #12

; Allocate memory for port_d

; GPIO port_d { STM32F407::GPIO_D };

:

08000d48: mov r0, sp : r0 = &port_u

08000d4a: movs r1, #3 : r1 = STM32F407::GPI0_D

0x8000cf8 : GPI0::GPI0()

; port_d.set_as_output(GPIO::Pin15);

08000d50: Idr r2, [sp, #4] ; r2 = registers

08000d52: Idr r3, [r2, #0] : r3 = registers->mode

08000d54: orr.w r3, r3, #1073741824 : r3 = r3 | 0x4000000

registers->mode = r3

08000d58: str r3, [r2, #0] ; registers->mode = r3

while(true) {

; port_d.set_pin(GPIO::Pin15);

loop:

08000d5a:

ldr

r3, [sp, #4]

; r3 = registers

08000d5c:

ldr

r2, [r3, #20]

; r2 = registers->output_data

08000d5e:

orr.w

r2, r2, #32768

; r2 = r2 | 0x8000

08000d62:

str

r2, [r3, #20]

; registers->output_data = r2

; port_d.clear_pin(GPIO::Pin15);

08000d64: Idr

r2, [r3, #20]

; r2 = registers->output_data

: }

```

Looks pretty familiar, doesn't it?

One final option with the structure overlay implementation: we can hide our implementation using the Pointer-to-Implementation (pImpl) idiom. Since we are simply declaring a pointer to a structure inside the class declaration the compiler is happy for that to be a pointer to an incomplete (that is, not-yet-defined) structure. The structure itself can be defined inside the implementation file.

```

class GPI0 {

public:

explicit GPI0(STM32F407::device dev);

~GPI0();

// Copy and move policy...

// Behavioural API...

private:

STM32F407::device ID;

// Pointer to incomplete type:

// struct Registers must be defined in

// the .cpp file

//

volatile struct Registers* const registers;

};

```

There is a price to pay for this, though. Our member functions are currently inlined for speed, and hence in the header file. Since the Registers structure is not defined in the header file any more we cannot refer to any of its members. Therefore, we cannot inline our member functions.

## Placement new

#### Structure overlay

If you're accessing a hardware I/O device with multiple registers it's very convenient (and efficient) to do so with a structure overlay. A structure is defined matching the layout of the hardware registers and this is 'overlaid' onto I/O memory using a pointer:

```

struct UART_Registers {

std::uint8_t tx;

std::uint8_t ctrl;

std::uint8_t rx;

std::uint8_t status:

};

```

(For the purposes of this example I'm going to assume 8-bit registers, consecutively in memory. This eliminates some of the potential pitfalls of structure overlay.

Of course, with a struct clients are free to manipulate any of the registers in ways that might not be appropriate or safe

```

int main()

{

auto const uart_ptr { reinterpret_cast<volatile UART_Registers*>(0x40021000) };

uart_ptr->ctrl = 0b00000001; // Is this valid?

uint8_t data { };

...

uart_ptr->rx = data; // What does this do?!

}

```

## **Class overlay**

Uncontrolled access to underlying hardware is unlikely to be a robust solution. Using a class allows us to provide encapsulated access to the hardware via member functions (the actual implementation of our UART is unimportant for this article).

```

class UART {

public:

UART():

~UART():

void write(uint8_t data):

private:

std::uint8_t tx;

std::uint8_t ctrl;

std::uint8_t rx;

std::uint8_t status;

};

```

```

UART::UART()

{

// Initialise and configure

// hardware for use...

}

uint8_t UART::read()

{

// Wait for data...

//

while((status & (1 << 3)) == 0) { }

return rx;

}</pre>

```

We can once again perform structure overlay. Now, we have protection for our registers and an abstract API to program to.

```

int main()

{

auto const uart { reinterpret_cast<volatile UART*>(0x40021000) }:

uart->ctrl = 0b00000001: // FAIL! => ctrl is private

uint8_t data { }:

...

data = uart->read(); // FAIL! Eh?

}

```

It should be no surprise that the first use of uart\_ptr fails – we are attempting to access a private member of the UART class.

The second failure is more perplexing. The read() function is marked as public, so this isn't the issue. The error message is also confusing:

no known conversion for implicit 'this' parameter from 'volatile UART\*' to 'UART\*'

#### cv-qualifers means const AND volatile

If you're familiar with const-correctness in your code this error should look familiar (If you're not familiar with const-correctness, here's a good overview - <u>https://isocpp.org/wiki/faq/const-correctness#overview-const</u>)

When we build const-correct classes we mark member functions as const if the only inspect the owning object; not modify it. Technically, marking a member function as const changes the type of the 'this' pointer to a const-pointer-to-const-type.

The thing is, this also holds true for volatile objects (that's why they're known as the *cv-qualifiers* and not the *c-qualifer* and *v-qualifer*!)

When we did our structure (class) overlay we declared the this pointer as a volatile UART\*. This is perfectly correct – since we are overlaying on hardware we don't want the compiler to optimise away any read/write operations.

Just as you cannot call a non-const member function on a const object, you cannot call a non-volatile member function on a volatile object!

Bizarre but true!

To fix this we would have to modify our UART class.

```

class UART {

public:

UART();

~UART ();

uint8_t read() volatile;

void write(uint8_t data) volatile;

private:

std∷uint8_t tx;

std∷uint8_t ctrl;

std∷uint8_t rx;

std∷uint8_t status;

};

UART::UART()

{

// Initialise and configure

// hardware for use...

}

uint8_t UART::read() volatile

{

// Wait for data...

//

while((status & (1 << 3)) == 0) \{ \}

return rx;

}

```

Now we get the behaviour we were expecting.

```

int main()

{

auto const uart { reinterpret_cast<volatile UART*>(0x40021000) };

uart->ctrl = 0b00000001; // FAIL! As expected

uint8_t data { }:

...

data = uart->read(); // OK

}

```

When we declare an object as volatile (either in its declaration or via a pointer) we are saying that all attributes of the class must be treated as volatile objects. Perhaps a cleaner way to specify this is to explicitly volatile-qualify our class members instead.

```

class UART {

public:

UART();

~UART();

uint8_t read();

```

```

void write(uint8_t data);

private:

volatile std::uint8_t tx;

volatile std::uint8_t ctrl;

volatile std::uint8_t rx;

volatile std::uint8_t status;

};

```

```

int main()

{

auto const uart { reinterpret_cast<UART*>(0x40021000) };

uart->ctrl = 0b00000001; // FAIL! As expected

uint8_t data { };

....

data = uart->read(); // OK

}

```

## **Placement new**

Our code now compiles (Quick! Ship it!) but it probably still won't work properly. The reason? The underlying hardware is not being initialised.

The initialisation code for our UART is (quite reasonably) in its constructor code. However, the constructor for the UART class is never being called!

Let's review this line of code:

auto const uart { reinterpret\_cast<volatile UART\*>(0x40021000) };

This code effectively says "treat the address 0x40021000 *as if there was a UART object at that location*". At no point is that UART object ever constructed (and hence initialised).

Enter placement new.

The default operator new allocates memory for an object, then calls its constructor. Placement new is an overload of operator new that does not allocate memory, but just constructs an object at a – provided – memory location.

The signature of placement new is:

void\* operator new(std::size\_t, void\*)

Note the placement new takes a second parameter – the address to construct the object at. It can be called like this

```

class ADT {

// ...

}:

static uint8_t pool[64]:

int main()

{

ADT* const adt { new(reinterpret_cast<void*>(pool)) ADT { } }:

....

}

```

(Note: To be more correct, I should have used static\_cast in the above code. I've stuck with reinterpret\_cast to avoid confusion with the rest of the paper)

We can make use of placement new to perform structure overlay on our hardware, and guarantee the constructor is called.

```

int main()

{

auto const uart { new (reinterpret_cast<void*>(0x40021000)) UART { } };

uart->read();

...

}

```

Notice we can't use constexpr here, since the UART is (as far as the language is concerned) a dynamic, not a compile-time, object (and we can't use reinterpret\_cast<> in constant-expressions).

## What about placement delete?

If we are using new, the usual idiom is to pair it with a call to delete. However, there is no *placement delete* (You can read a discussion on the topic here - <a href="http://stackoverflow.com/questions/5857240/why-there-is-no-placement-delete-expression-in-c">http://stackoverflow.com/questions/5857240/why-there-is-no-placement-delete-expression-in-c</a>)

Don't be tempted to call operator delete on your placement new'd object, either. The behaviour of delete is to call the destructor on the object, then free the memory associated with the (provided) pointer. In our case, that memory is somewhere in the I/O space! The chances of that ending well are slim-to-none!

If you want to ensure your class's destructor is called you must call it explicitly:

```

int main()

{

auto const uart { new (reinterpret_cast<void*>(0x40021000)) UART { } };

uart->read();

...

uart->~UART(); // Explicitly call destructor for cleanup.

}

```

#### Other limitations of class overlay

This is all looking very neat but there are a couple of important limitations on using classes for hardware memory overlay:

- You can't have virtual functions on the class

- The class can't have any additional attributes, beyond the registers

Think about where our overlay object is being constructed: I/O memory. This is not normal memory. It does not consist of consecutive bytes of data memory. Attempting to store additional attributes will cause them to be read from / written to undefined memory:

- Possibly other hardware registers, where they could randomly change, according to the whims of the underlying hardware device;

- They could corrupt the operation of hardware devices

- Writing to undefined memory locations could (silently)fail or produce junk values

- Putting attributes in the wrong place in the class declaration could 'slew' the hardware overlay layout

Virtual functions require the use of a virtual table pointer as part of the object. This pointer is implicitly added to the object by the compiler; normally at the object's base address. This pointer would (probably) be overlaid on a hardware register (which might be changing!) or in undefined memory. Neither of these is likely to end well for virtual function calls made on the object!

# Generic register types

As code designers we tend to eschew specific 'stove-pipe' code in favour of reusable code elements. Up until now we've been coding some very specific examples so it's probably worth looking at some more generic solutions.

Now we'll look at building generic register manipulation classes (or 'register proxy' classes if you prefer). We're really exploring code design rather than coding 'mechanics'. I'm using this to explore some factors like the balance between efficiency, performance and flexibility.

## A first-pass design

Our previous designs have focussed on building abstractions of I/O devices – GPIO ports, UARTs, etc. This time we will focus on a class that represents a single hadware register. Here's a first-pass design. This is not a complete interface by any stretch. I'm deliberately ignoring most of the API for clarity. We've discussed interface design in detail earlier.

```

class Register {

public:

explicit Register(std::uint32_t address);

Register& operator=(std::uint32_t bit_mask);

operator uint32_t();

inline Register& operator|=(std::uint32_t bit_mask);

inline Register& operator&=(std::uint32_t bit_mask);

inline Register& operator^=(std::uint32_t bit_mask);

// etc...

private:

volatile std::uint32_t* raw_ptr;

};

```

The constructor maps the internal raw\_ptr onto the supplied address.

```

Register::Register(std::uint32_t address) :

raw_ptr { reinterpret_cast<std::uint32_t*>(address) }

{

}

```

Operations on the Register class are mapped directly onto the hardware

```

Register& Register::operator|=(std::uint32_t bit_mask)

{

*raw_ptr |= bit_mask:

return *this:

}

```

Clients can now use Register objects as proxies for hardware registers

```

int main()

{

Register mode { 0x40020C00 };

Register output { 0x40020C14 };

```

```

mode |= (1 << (15 * 2));

output |= (1 << 15);

output &= ~(1 << 15);

....

```

There's a limitation with this class at the moment: it only handles 32-bit registers. For flexibility we'd like to be able to support 8-bit, 16-bit and 32-bit registers. We could provide multiple classes, for example:

```

class Register_32 {

// As above.

};

class Register_16 {

// As above, but for uint16_t.

};

class Register_8 {

// You get the idea...

};

```

There's a huge amount of code repetition here. The design is crying out for a generic solution.

#### Second attempt: template-based solution

Let's make our Register class a template. But what's the template parameter? Let's start by making it the underlying register type

```

template <typename T>

class Register {

public:

explicit Register(std::uint32_t address);

Register& operator=(T bit_mask);

operator T();

inline Register& operator&=(T bit_mask);

inline Register& operator^=(T bit_mask);

inline Register& operator^=(T bit_mask);

// etc...

private:

volatile T* raw_ptr;

};

```

Our client code changes, now

```

int main()

{

Register<std::uint32_t> mode { 0x40020C00 };

Register<std::uint32_t> output { 0x40020C14 };

mode |= (1 << (15 * 2));

output |= (1 << 15);

output &= ~(1 << 15);

....

}</pre>

```

This is fine; but it doesn't prevent awkward client code like this:

```

int main()

{

Register<int> mode { 0x40020C00 };

Register<int> output { 0x40020C14 };

// What happens when you perform bitwise

// operations on signed numbers?

//

mode |= (1 << (15 * 2));

output |= (1 << 15);

output &= ~(1 << 15);

...

}</pre>

```

## Third attempt: Using a template trait class

An alternative approach is to encapsulate the type of the pointer and just allow the client to specify the number of bits in the register.

This gives us an implementation problem: what's the type of the underlying raw pointer?

```

template <std::size_t sz>

class Register {

public:

explicit Register(std::uint32_t address);

Register& operator=(??? bit_mask);

operator ???();

inline Register& operator=(??? bit_mask);

inline Register& operator&=(??? bit_mask);

inline Register& operator^=(??? bit_mask);

```

For an 8-bit register the pointer-type should be (something like) std::uint8\_t; for a 16-bit register it should be std::uint16\_t; and so on. How can we deduce the type just from the number of bits?

The solution is to use a template trait class. A trait class acts as a compile-time lookup for typespecific (or, in our case, value-specific) characteristics.

```

template <unsigned int sz>

struct Register_traits { };

template \diamond

struct Register_traits<8> { using internal_type = std::uint8_t; };

template \diamond

struct Register_traits<16> { using internal_type = std::uint16_t };

template \diamond

struct Register_traits<32> { using internal_type = std::uint32_t; };

template \diamond

struct Register_traits<64> { using internal_type = std::uint64_t; };

template <std::size_t sz>

class Register {

public:

// Type alias for convenience

11

using reg_type = typename Register_traits<sz>::internal_type:

explicit Register(std::uint32_t address);

Register& operator=(reg_type bit_mask);

operator reg_type();

inline Register& operator |=(reg_type bit_mask);

inline Register& operator&=(reg_type bit_mask);

inline Register& operator^=(reg_type bit_mask);

// etc...

private:

volatile reg_type* const raw_ptr; // <= Register_traits<sz>::internal_type

};

```

When a Register template class is instantiated the sz template parameter is used to select an appropriate trait class specialisation. The trait class's internal\_type alias is used to provide the reg\_type alias for the Register class.

```

int main()

{

Register<32> mode { 0x40020C00 }; // <= std::uint32_t

Register<16> output { 0x40020C14 }; // <= std::uint16_t

Register<17> odd { 0x40021000 }; // FAIL - No trait for 17-bit

}

```

Thus, a Register<32> will have its reg\_type set as std::uint32\_t; a Register<16> will have its reg\_type declared as std::uint16\_t.

If an arbitrary number is selected, for example Register<17>, the code will fail to compile as there is no appropriate trait class.

## Under the hood

What's the cost of this template complexity in terms of run-time performance? We'll use a variation on code we've used before.

```

#include "Register.h"

namespace STM32F407 {

enum device {

GPIO_A, GPIO_B, GPIO_C,

GPIO_D, GPIO_E, GPIO_F,

GPIO_G, GPIO_H, GPIO_I

};

inline void enable_device(device dev)

{